適応型演算アクセラレーションによるコアインフラストラクチャのパフォーマンス向上

コネクティビティが最適化された ACAP

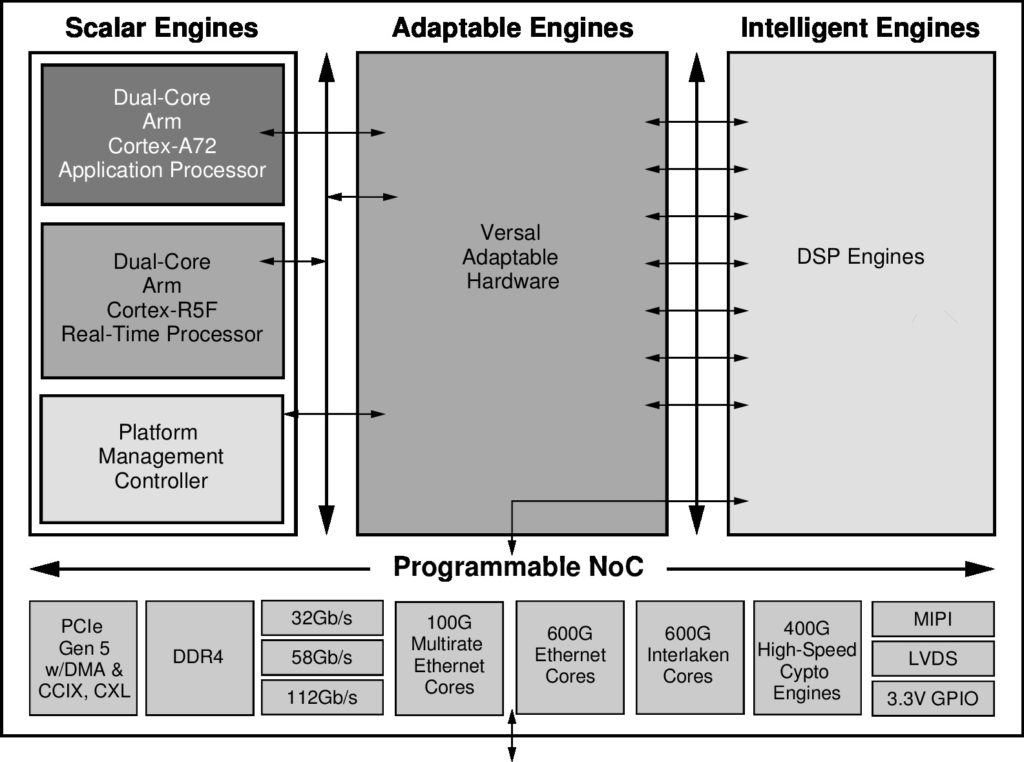

Versal プレミアムシリーズは、この新しいクラスのプログラマブル デバイスによって確立されたイノベーションをベースとして、今日のコア インフラストラクチャへの需要に対処するべく誕生しました。この高帯域幅デバイスは、高い演算密度に加えて、専用高速暗号化 (HSC) エンジンおよび最新のネットワーク インターフェイスを兼ね備えています。

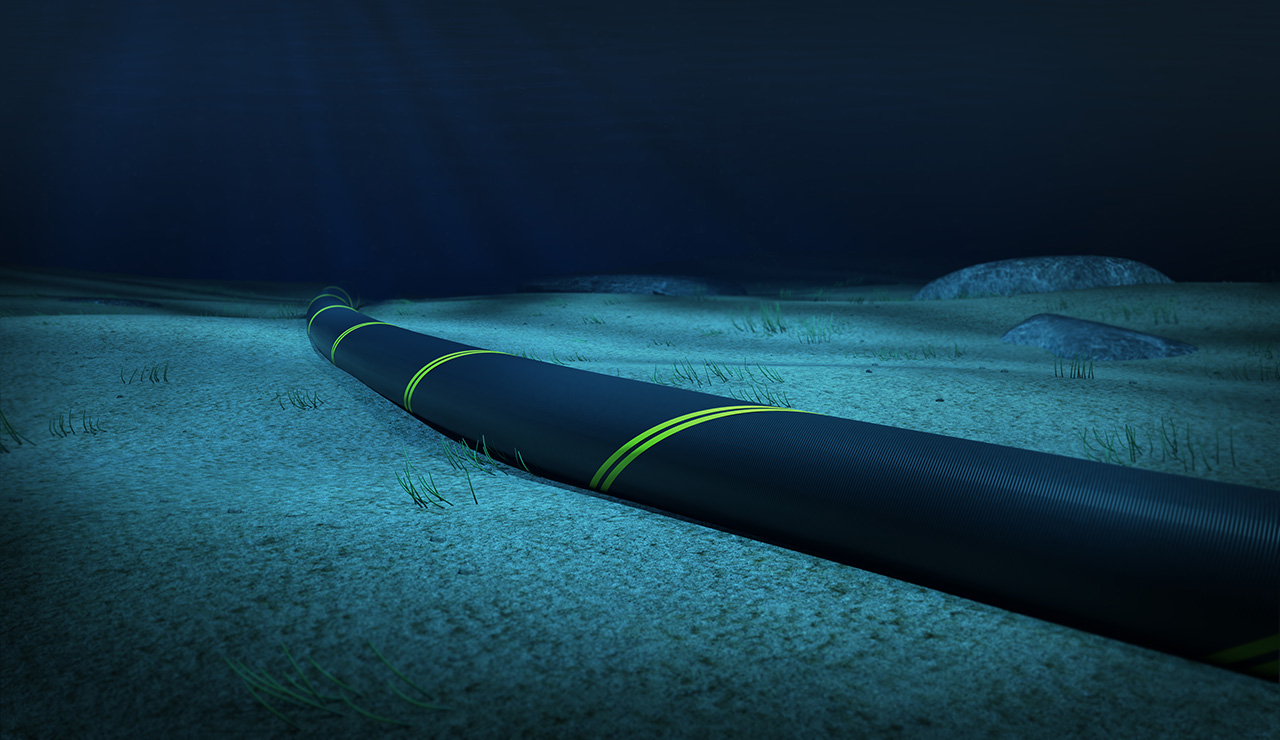

これらのネットワーク コネクティビティには、双方向帯域幅合計 9Tb/s まで拡張可能な光トランシーバーが含まれており、最新のイーサネットおよび Interlaken の速度とプロトコル、112Gb/s の PAM4 トランシーバー、最大 400Gb/s の高速暗号化エンジンによる暗号処理、適応型ハードウェアをサポートします (図 1)。

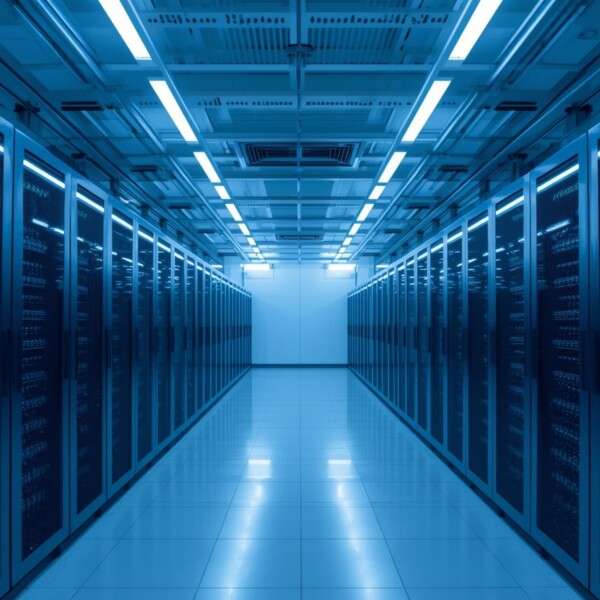

112G PAM4 トランシーバーをコア インフラストラクチャ、メトロ インフラストラクチャ、DCI インフラストラクチャに使用すると、既存の 58Gb/s PAM4 テクノロジと比べてポートあたりの帯域幅密度が倍増し、それによりフロントパネルの占有ラック スペースを減らすことができ、通信アプリケーションやデータセンター アプリケーションのユニットあたりの帯域幅を 2 倍にできます。同時に、所定のデータ ペイロードを送信する際のレイテンシが 50% 低くなるため、アプリケーションの応答性が向上し、地理的に分散されたデータセンターを相互接続する際のレイテンシの影響を軽減できます。

リソースをチップ上で統合することで、ザイリンクス 16nm Virtex® UltraScale+™ FPGAの最大 3 倍の帯域幅、2 倍の演算密度を提供します。一方、アプリケーション固有の専用 OTN (光トランスポート ネットワーク) プロセッサと比べて、アプリケーションのスループットは 3 ~ 5 倍になります。

演算密度の向上

ハイパースケール クラウド サービス プロバイダーの現在および将来の需要に対応するため、Versal ACAP アーキテクチャは、高性能ヘテロジニアス演算エンジンと密結合された非常に高いオンチップ メモリ帯域幅と、Dynamic Function eXchange (DFX) による柔軟なワークロード プロビジョニングを兼ね備えています。DFX は前述の 16nm FPGA に比べて 8 倍の速さでカーネルを切り替えることができ、アクセラレーターを動的にプロビジョニングして、データ解析、機械学習のビジョン処理、ゲノミクス、ビデオ トランスコーディング、暗号処理といった経時変化する演算ワークロード用のデバイス リソースを最大限効率的に利用することを可能にします。

さまざまなタイプの分散型オンチップ RAM を搭載していることで、最大 1Gb の密結合メモリが利用可能となり、オンチップ メモリ帯域幅は最大 123TByte/s に相当します。これにより、現在最高の GPU よりも 9 倍高速な、各種処理エンジンとメモリ間の高速な相互接続が可能になります。加えて、プログラマブル NoC インターコネクトにより、オフチップの DDR4 メモリとの高速な相互接続もサポートされます。

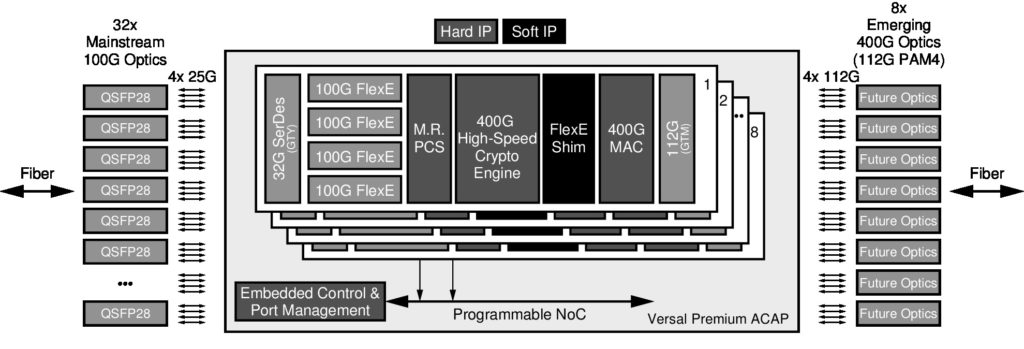

Versal プレミアム ACAP は、セキュアでコスト効率の高いプラットフォームで新しい規格や発展途中の規格に適応できる柔軟性を持ちながら、サーバー側およびトランスポート側のさまざまな光モジュールやプロトコルに対応したいという、DCI 機器に対するニーズを満たすことができます。1RU システムまたはシングル カードだけで、幅広い標準および最新プロトコルや光モジュールをサポートした 3.2Tb/s が実現されます (図 2)。最新のコネクティビティと暗号コアを備えた Versal プレミアム ACAP 1 つで、サーバー側の光モジュールとの 4x25G NRZ 接続を使用した複数の 100G FlexE イーサネット チャネル、4x112G PAM4 接続で実装されたライン側の 400G イーサネット チャネル、1.6Tb/s ライン レートの AES256 暗号化、制御機能およびポート管理機能の実装が可能です。

コメント ( 0 )

トラックバックは利用できません。

この記事へのコメントはありません。