Intel、AMD、Arm、GoogleなどがUCIeコンソーシアムを設立

チップ設計企業、サプライヤー、メーカー、およびハイパースケールユーザーらが、チップレットコンソーシアムの結成に向けて結集しました。

Universal Chiplet Interconnect Express (UCIe)コンソーシアムでは、ダイ間インターコネクト規格を策定し、「オープンチップレットエコシステムを育成する」としています。

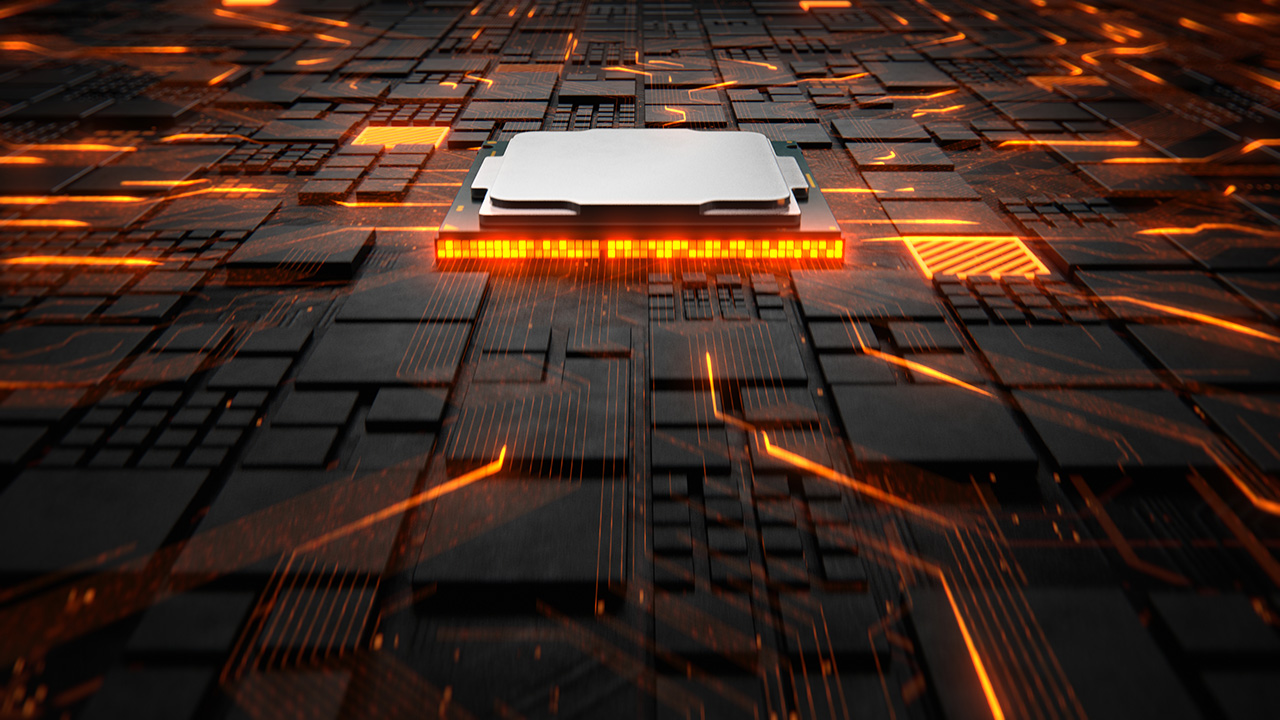

半導体設計業界では、1つのモノリシックなダイの代わりに小さなダイを使用する「チップレット」という概念が広まっています。

半導体設計業界では、1つのモノリシックなダイの代わりに小さなダイを使用する「チップレット」という概念が広まっています。

これまでチップレットは、CPUをいくつかのピースに分割するために使われてきました(極端な話、Intel Ponte Vecchioは1つのパッケージに47個のチップレットを搭載)。しかし、相互運用性があれば、異なるメーカーのチップレットを混在させたチップを作ることができます。

IntelとAMDは以前、「Intel 8th Generation Core with Radeon RX Vega M Graphics」というチップで、「Hシリーズ」のIntelのCPUとAMD Radeonグラフィックス・プロセッサを2チップで同一パッケージに搭載する試みを行っていましたが、真の相互運用性には欠けています。

UCIeはこの問題の解決を目的としており、少なくとも参加企業にとってはそうです。

このコンソーシアムは、Advanced Semiconductor Engineering, Inc.(ASE)、 AMD、Arm、Google Cloud、Intel 、Meta、Microsoft 、Qualcomm、 Samsung、そしてTSMCを設立メンバーとして発足しました。

尚、NvidiaとAWSは現在メンバーではありません。

UCIe仕様とは、パッケージレベルでのユビキタス・インターコネクトを確立するために開発されたオープンな業界標準仕様です。UCIe 1.0仕様は、ダイからダイへのI/O物理層、ダイからダイへのプロトコル、そしてPCI ExpressおよびCompute Express Link規格を活用したソフトウェアスタックを対象としています。

Intelのデータセンター&AI部門担当副社長兼GMのSandra Rivera氏は、「複数のチップレットをパッケージに統合して市場セグメントにわたる製品イノベーションを実現することは、半導体業界の未来であり、IntelのIDM 2.0戦略の柱である」と述べています。

一方、Meta(旧Facebook)の技術・戦略担当ディレクターであるVijay Rao氏は、次のように述べています。「Metaは、Open Compute Project(OCP)を介してチップレットベースSOCの普及に向け、エコシステム開発を開始し、またこの分野での継続的かつ将来の成功に向けて、UCIeコンソーシアムを通じて他の業界リーダーと協力していけることを嬉しく思う」

この記事は海外Data Centre Dynamics発の記事をData Center Cafeが日本向けに抄訳したものです。

コメント ( 0 )

トラックバックは利用できません。

この記事へのコメントはありません。