Google、AIを活用しチップ設計を高速化

Googleは、マイクロチップの設計に必要な要素を機械学習システムに学習させることで、人間よりもはるかに効率的かつ迅速に、省スペース、省電力、高性能化を実現できると発表しました。

Googleはすでにこの技術を、Tensor Processing Units(TPU)などの量産チップにメモリブロックを配置するために使用していると述べています。今週、科学雑誌「Nature」に、Azalia Mirhoseini氏が率いるチームが、チップのいわゆる「フロアプラン」にグラフ配置を利用した論文が掲載されました。

Nature誌はオピニオン記事の中で、チップ設計の自動化は将来のハードウェア世代を加速させる可能性があるとしながらも、次のように警告しています。「しかし、企業の “エコシステム “が真の意味でグローバルなものになるためには、技術的な専門知識を広く共有する必要がある。また、業界としては、時間短縮のための技術が、必要なコアスキルを持つ人々を遠ざけないようにしなければならない」

優れたチップ設計

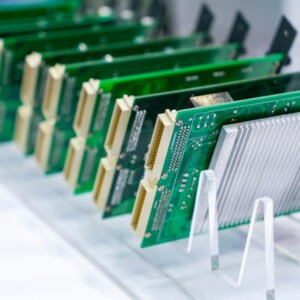

シリコンチップは複数のコンポーネントから構成されていますが、その物理的なレイアウトを設計する「フロアプラン」は複雑な作業です。Googleは、AIシステムに1万パターンの設計を見せ、効率と性能の評価を行いました。その結果、6時間後には、人間が数ヶ月かけて設計したものと同等以上のチップの設計が可能になったとしています。

AIは、この問題をゲームのように捉え、盤面に駒を置き、勝利を掴むような設定がなされていました。ゲームに例えると、囲碁が約10360通りの構成(状態空間)を持つのに対し、チップの状態空間は102,500通りと、102000倍以上も複雑です。

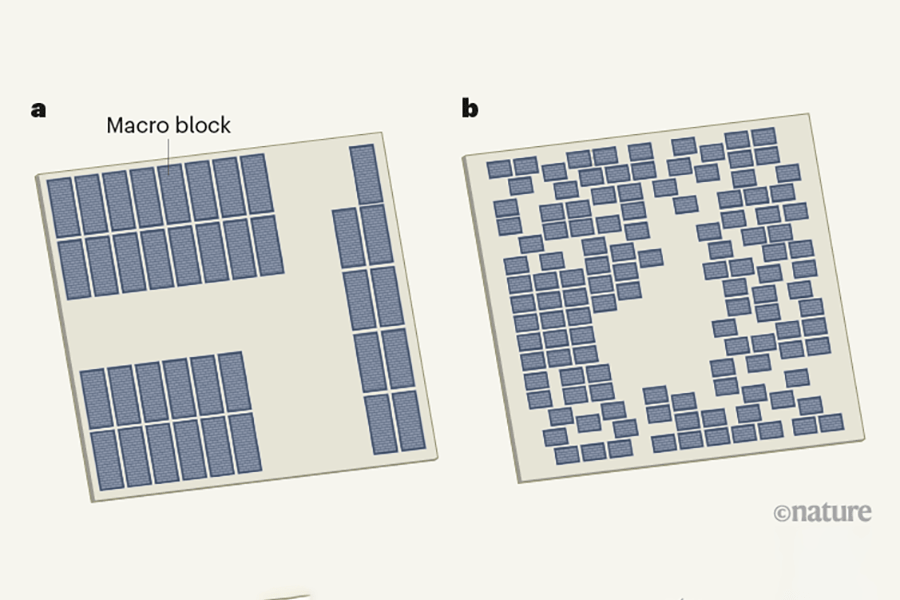

このシステムでは、まず大きな単位である「マクロブロック」を配置し、その周りのスペースを小さなセルで埋めていきましたが、その結果は少々意外なものでした。Nature誌に掲載された論文をもとに作成されたこのダイアグラムは、メモリ用のマクロブロックの配置を示しています。a – 人間が設計したRISC-Vプロセッサ「Ariane」では、マクロブロックが整然と並び、その間に小さなコンポーネントが配置されています。一方、bでは、GoogleのAIが、メモリブロックの配置を変えてグループ化することで、性能を向上させ、関係するすべてのセルのより適切な配置を実現しています。

この論文は、昨年Arxivサイトにプレプリントとして初めて公開され、GoogleのAI責任者ジェフ・ディーン氏は、2020年2月に開催されたInternational Solid-State Circuits Conference(ISSCC:半導体集積回路技術に関する国際会議)の基調講演でこの技術を説明しました。それに続いてGoogleは、この手法を現在のTensor Processing Units(TPU)の設計などのチップ開発に利用していることを明らかにしました。

「我々の手法は、Googleの次世代の人工知能(AI)アクセラレータの設計に使用され、新世代ごとに数千時間の人間の労力を削減できる可能性を秘めている」と、著者はその要旨で述べています。「最後に、我々は、より強力なAI設計のハードウェアがAIの進歩を促進し、この2つの分野の間に共生関係が生まれるものと信じている」

Data Center Dynamics

コメント ( 0 )

トラックバックは利用できません。

この記事へのコメントはありません。